Hardware Design Dataset for Circuit Graph Analysis

- Citation Author(s):

-

Rozhin Yasaei (University of California Irvine)Shih-Yuan Yu (University of California Irvine)Qingrong Zhou (University of California Irvine)Mohammad Abdullah Al Faruque (Mohammad Abdullah)

- Submitted by:

- Rozhin Yasaei

- Last updated:

- DOI:

- 10.21227/j1vv-hw18

- Data Format:

2849 views

2849 views

- Categories:

- Keywords:

Abstract

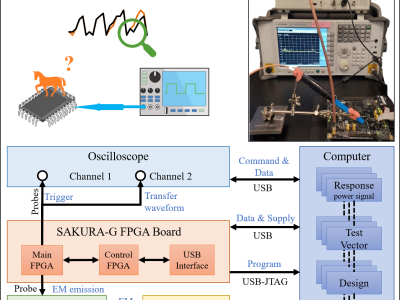

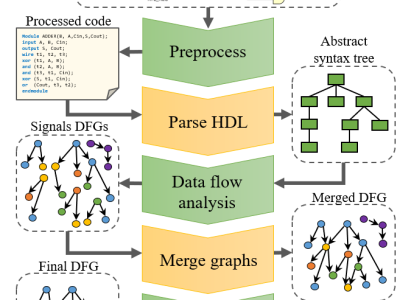

The time-to-market pressure and the continuous growing complexity of hardware designs have promoted the globalization of the Integrated Circuit (IC) supply chain. However, such globalization also poses various security threats in each phase of the IC supply chain. Although the advancements of Machine Learning (ML) have pushed the frontier of hardware security, most conventional ML-based methods can only achieve the desired performance by manually finding a robust feature representation for circuits that are non-Euclidean data. As a result, modeling these circuits using graph learning to improve design flows has attracted research attention in the Electronic Design Automation (EDA) field. However, due to the lack of supporting tools, only a few existing works apply graph learning to resolve hardware security issues. We propose this dataset along with HW2VEC, an open-source graph learning tool that lowers the threshold for newcomers to research hardware security applications with graphs. HW2VEC provides an automated pipeline for extracting a graph representation from a hardware design in various abstraction levels (register transfer level or gate-level netlist). Besides, HW2VEC users can automatically transform the non-Euclidean hardware designs into Euclidean graph embeddings for solving their problems. This dataset includes the Verilog files of different hardware designs and the data-flow graphs that the HW2VEC tool is generated for each circuit.

If you find our dataset useful in your research, please cite our papers:

@inproceedings{yasaei2021gnn4tj, title={GNN4TJ: Graph neural networks for hardware Trojan detection at register transfer level}, author={Yasaei, Rozhin and Yu, Shih-Yuan and Al Faruque, Mohammad Abdullah}, booktitle={2021 Design, Automation \& Test in Europe Conference \& Exhibition (DATE)}, pages={1504--1509}, year={2021}, organization={IEEE} }

@article{yu2021hw2vec, title={HW2VEC: A Graph Learning Tool for Automating Hardware Security}, author={Yu, Shih-Yuan and Yasaei, Rozhin and Zhou, Qingrong and Nguyen, Tommy and Faruque, Mohammad Abdullah Al}, journal={arXiv preprint arXiv:2107.12328}, year={2021} }