Dataset Entries from this Author

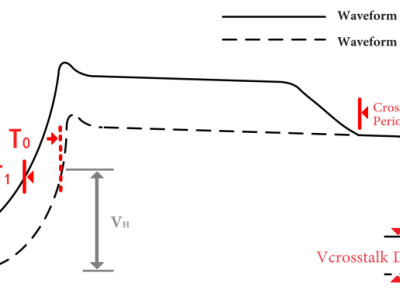

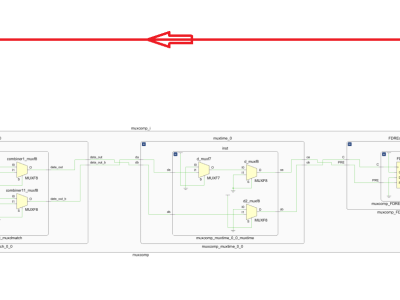

This project is used to examine the actual resolution of a cross talk based TDC. In which, the ZYNQ core is used to provide a reference clock after device start-up. In the meantime, the IDELAY instance inside the LOOP MUX can be adjusted at different tap counts to find out the TDC's resolution. Where, the IDELAY tap delay is determined by comparing it with the reference clock. To be more specific, a crystal clock pulse is brought into the TDC loop by the MMCM.

- Categories:

- Categories:

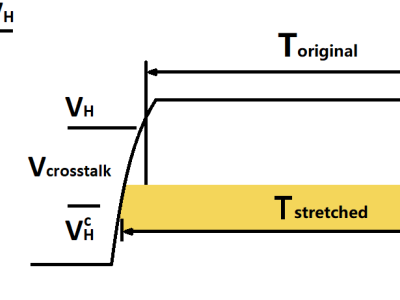

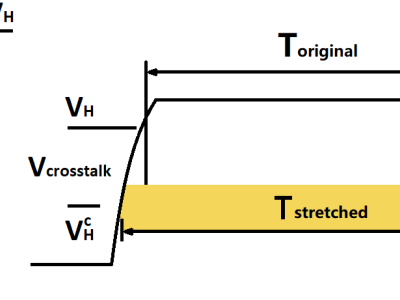

A Pulse Stretching Time to Digital Converter(TDC) exploits the crosstalk effect on FPGA. The principle idea is to superpose an induction voltage on the sense line to lower its logic toggling voltage while maintaining the other parameters intact.

- Categories:

A demo for examing the Pulse Shrinking TDC's external capturing performance.

- Categories:

TDC demo for ps level mannual calibration

- Categories:

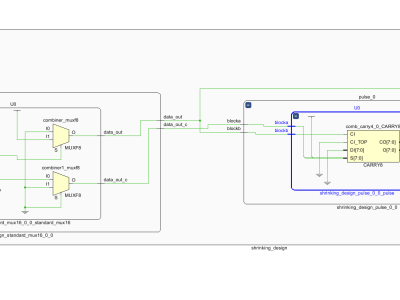

This design is a Pulse Shrinking TDC with 2ps resolution, which is reduced to 7 CLBs.

- Categories:

Pulse Shrinking TDC utilizing the FPGA cell block Architecture. Ultra Compact Design.

- Categories: