Datasets

Standard Dataset

A Novel SOI-LDMOSFET With Superior Electrical Performances

- Citation Author(s):

- Submitted by:

- Mohammadreza Gh...

- Last updated:

- Sun, 10/11/2020 - 02:11

- DOI:

- 10.21227/rpz9-vd50

- Data Format:

- License:

Abstract

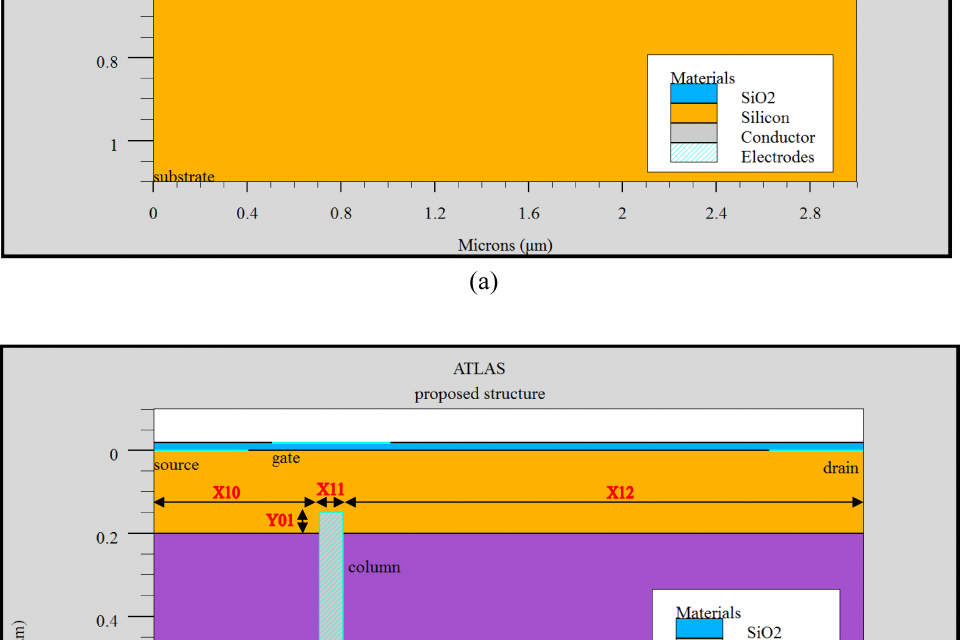

In current study, a new silicon-on-insulator (SOI) lateral-double-diffused metal-oxide-semiconductor field-effect transistor (LDMOSFET) is offered. Altering charge distribution causes less electric field crowding and enhanced breakdown voltage (VBR). For amending charge distribution, a metal region (COLUMN) and an air layer in the transistor are used. On the other the floating-body influence and impact ionization produce additional holes that are intensified via the parasitic bipolar junction transistor (BJT) in SOI-LDMOSFET that weaken the transistor efficiency. For that matter, a silicon layer under the BOX, attached to the channel area through the COLUMN has been replaced for reducing the hole density in the channel and control the BJT impact considerably. In order to attain the optimal outcomes, the COLUMN and the silicon layer under the BOX location and sizes are optimized carefully. DC and radio frequency features corresponding to the offered structure are examined through 2-D numerical simulation and compared with conventional SOI-LDMOSFET (C-SOI-LDMOSFET) features. The VBR corresponding to the offered structure develops by 229% comparing with that of the C-SOI-LDMOSFET structure. Though drain current of the suggested structure decreases slightly, 220% development in utmost output power density for the device is attained because of great enhancement of the VBR. Furthermore, the suggested structure causes the development of utmost oscillation frequency, utmost existing gain, and selfheating impacts corresponding to the device. Consequently, the suggested structure has excellent electrical performances comparing with the analogous device according to the conventional structure.

Recently, silicon-on-insulator (SOI) technology has been widely used in high-speed and low-power consumption applications. Structures of SOI have significant benefits including low leakage current, more switching speed, significant decrease in parasitic capacitance (low junction capacitance) for power and high voltage ICs, latch-up immunity, and developed device isolation due to using the buried oxide (BOX) [1]-[2]. Additionally, they have the benefit of being compatible with mainstream CMOS processing. The SOI CMOS is a cheap technology that can be utilized for radio frequency (RF) integrated circuits due to its capability for merging RF circuits and digital logic on a single chip [3]–[5]. In many studies, lateral double-diffused MOSFETs (LDMOSFET) on SOI have been widely used as the procedures are simple to merge with other devices and are also well-matched with the BiCMOS technology [6]. Two main benefits of the SOI-LDMOSFET are low ON-resistance and high breakdown voltage. Though, the parasitic bipolar junction transistor (BJT) because the floating-body effect is more harmful in such devices and must be controlled. Different solutions have been suggested to decrease the floating-body effect and the parasitic BJT effect [7]–[10].

The floating-body effect and impact ionization produce extra holes that are intensified with the parasitic BJT in the SOI-LDMOSFET and reduce their efficiency. If we could absorb the produced holes from the impact ionization mechanism in the SOI-LDMOSFET, that time, complete absence of the hole density in the channel and a considerably reduced BJT impact with no effect on the ON-state current occur. In an article has suggested a silicon germanium (SiGe) window under the channel area to decrease the thickness of BOX in which the SiGe window under the channel area can absorb and resynthesize the effect created holes to suppress the floating-body impact and develop the breakdown voltage [11].

In SOI technology, SOI lateral double-diffused metal–oxide–semiconductor field-effect transistor (LDMOSFET) has been widely studied and used. Their mobility, which is also referred to as surface mobility, is less comparing with half of the bulk material mobility because of the wave function of carriers located in the inversion layer of a SOI-LDMOSFET structure that extends into the oxide. Higher mobility causes more transconductance (gm), current, and frequency factors of the device [12].

On account of the several developments in analyzing and developing the SOI-LDMOSFET features, a number of main surveys have been carried out on the structure of SOI-LDMOSFET. The distribution of charge has a main role in determination of device features [13]–[16]. In a study for altering the distribution of charge, a metal area is applied in the BOX of the offered structure [17]. Among the features of my study is to modify charge distribution of the bulk and particularly channel area in order to lower the electric field of the device and progress the VBR. For varying the distribution of charge, a metal column (COLUMN) is applied in the BOX of the offered structure, which is only from the air, also in current study, I have offered a silicon layer under the BOX layer that silicon layer via the metal column is able to absorb and resynthesize the impact created holes for suppressing the floating-body effect [18].

In current study, the self-heating impact as another difficulty in the SOI-LDMOSFET has been studied. The self-heating impact takes place as a result of the poor thermal conductivity of the BOX and reduces the device efficiency in the SOI technology. In previous efforts, many new devices have been suggested to control these penalties [19]–[21], including partial SOI in which the BOX is patterned for having a silicon window that attaches the active area to the substrate proposing a heat conduction path [19]. Therefore, decreased self-heating impacts and large breakdown voltage can be attained [19].

Therefore, in current study, I present a new SOI-LDMOSFET structure with a COLUMN in the transistor’s BOX that all of the BOX is air and with a silicon layer under the BOX. After using the COLUMN and silicon layer under a BOX full of air in the structure and optimization of their place and sizes, the offered SOI-LDMOSFET features including hole concentration, distribution of electric field, VBR, distribution of potential, drain current (ID), density of output power, unilateral power gain (U), maximum available gain (MAG), and current gain (fT ) are studied. The purpose of the suggested structure is to acquire a high-power and high-speed device also the suggested structure set is able to ease self-heating and control the floating-body impact considerably. It has shown that suggested structure attained significant developments in terms of the breakdown voltage, self-heating impacts, and gate capacitance by utilizing 2-D device simulation.

Documentation

| Attachment | Size |

|---|---|

| 6.08 MB | |

| 3.18 MB |

403 Views

403 Views

Comments

0000