Double-delay voltage-controlled oscillator chaotic integrated circuit data set

- Citation Author(s):

-

Huwei WANG

- Submitted by:

- huwei wang

- Last updated:

- DOI:

- 10.21227/dpg4-tc83

74 views

74 views

- Categories:

- Keywords:

Abstract

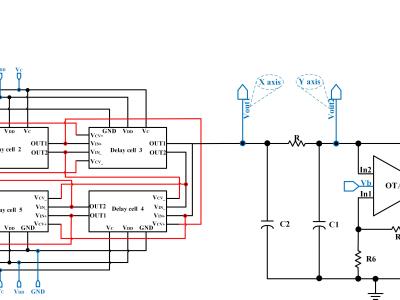

This paper presents a chaotic integrated circuit based on a dual-delay voltage-controlled oscillator (VCO). To address the hardware limitations associated with the traditional Chua circuit using discrete components, the proposed circuit employs the SMIC 180 nm CMOS process to achieve full integration. A dual-delay VCO regulates the oscillation frequency, while an operational trans-impedance amplifier (OTA) controls the gain within the circuit. The chaotic behavior of the integrated circuit is evaluated using Lyapunov exponents, bifurcation diagrams, and phase diagrams. Additionally, Monte Carlo simulations are conducted to verify the robustness of the chaotic characteristics under parameter variations and manufacturing tolerances. Under a 1.8 V power supply, the dual-delay VCO achieves an output frequency range from 426 MHz to 144 MHz. The circuit demonstrates exceptional performance, including a power consumption of 0.20408 mW, a gain bandwidth product (GBW) of 1.13 GHz, a compact footprint of 0.013038 mm², and a Lyapunov exponent ranging from 1.1106 to 2.421. Experimental findings and Monte Carlo analyses confirm the strong chaotic attributes and reliability of the dual-delay VCO-based chaotic integrated circuit. This design is distinguished by its low power consumption, small physical size, rapid response, and high stability, making it highly suitable for a wide range of applications.

Instructions:

The documentation for this design includes the following files:

1. .SP file: Specifies the parameter values used in the design, containing the key settings for circuit simulation;

2. .LIS file: Records the operational data of the integrated chaotic circuit, including the results generated during simulation;

3. .CDL file: Describes the dimensions and specific structural information of the transistors used in this design.

These files collectively form the core components of the design, providing comprehensive data support for the simulation, analysis, and implementation of the chaotic circuit.