Datasets

Standard Dataset

基于自注入锁定和环内混合技术的低相位噪声PLL设计

- Citation Author(s):

- Submitted by:

- Chen Qing

- Last updated:

- Fri, 08/09/2024 - 10:46

- DOI:

- 10.21227/24ks-ww62

- License:

26 Views

26 Views- Categories:

- Keywords:

Abstract

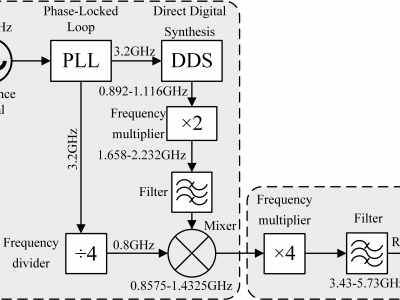

Abstract—This paper proposes an enhanced scheme for a traditional phase-locked loop (PLL) frequency synthesizer based on the integration of self-injected locking and in-loop mixing (SIL-MIX) techniques. This approach significantly reduces the overall phase noise of the conventional PLL frequency synthesizer. Additionally, the integration of a programmable phase shifter on the system provides a novel perspective for the on-board implementation of frequency synthesizers. Experimental results demonstrate that this method effectively reduces both near-end and far-end phase noise of the frequency synthesizer. The developed frequency synthesizer using the SIL-MIX loop exhibits a maximum phase noise reduction of up to 19 dB. The substantial decrease in phase noise enables the developed frequency synthesizer to achieve extremely low phase noise levels of -108, -110, and -136 dBc/Hz at offset frequencies of 10 kHz, 100 kHz, and 1 MHz, respectively.

This work was supported in part by the National Natural Science Foundation of China (61801262), the Open Research Programme of the State Key Laboratory of Millimeter Wave (K202312), and the Start-up Fund for Introducing Talents of Nanjing University of Information Engineering (2022r071). (Corresponding author:Hai Peng Wang)

The authors are with theResearch Center of Applied Electromagnetics, Nanjing University of Information Science & Technology, Nanjing 210044, China(e-mail:003551@nuist.edu.cn). Lin Yang is with 63rd Research Institute, National University of Defense Technology, Nanjing, China. F. He is with Nanjing Yao Meng Technology Co., LTD, Nanjing 211111, China.

Abstract—This paper proposes an enhanced scheme for a traditional phase-locked loop (PLL) frequency synthesizer based on the integration of self-injected locking and in-loop mixing (SIL-MIX) techniques. This approach significantly reduces the overall phase noise of the conventional PLL frequency synthesizer. Additionally, the integration of a programmable phase shifter on the system provides a novel perspective for the on-board implementation of frequency synthesizers. Experimental results demonstrate that this method effectively reduces both near-end and far-end phase noise of the frequency synthesizer. The developed frequency synthesizer using the SIL-MIX loop exhibits a maximum phase noise reduction of up to 19 dB. The substantial decrease in phase noise enables the developed frequency synthesizer to achieve extremely low phase noise levels of -108, -110, and -136 dBc/Hz at offset frequencies of 10 kHz, 100 kHz, and 1 MHz, respectively.

This work was supported in part by the National Natural Science Foundation of China (61801262), the Open Research Programme of the State Key Laboratory of Millimeter Wave (K202312), and the Start-up Fund for Introducing Talents of Nanjing University of Information Engineering (2022r071). (Corresponding author:Hai Peng Wang)

The authors are with theResearch Center of Applied Electromagnetics, Nanjing University of Information Science & Technology, Nanjing 210044, China(e-mail:003551@nuist.edu.cn). Lin Yang is with 63rd Research Institute, National University of Defense Technology, Nanjing, China. F. He is with Nanjing Yao Meng Technology Co., LTD, Nanjing 211111, China.

More from this Author